作者:Xie M. X. (UESTC,成都市)

晶体管有三种工作状态(工作模式)。

☆晶体管的放大状态--------

晶体管的工作状态(或工作模式)有放大状态、截止状态、饱和状态和反向放大状态四种.放大状态就是输出电流与输入电流或者与输入电压成正比的一种工作状态。在输出伏安特性曲线上,放大状态所处的范围对于BJT和FET有所不同。

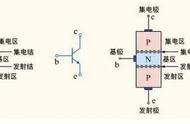

(1)对于BJT:

BJT的放大状态一般就是发射结正偏、集电结反偏的一种工作状态。因为BJT是电流控制的器件,故放大状态的输出电流与输入电流成正比。放大性能用电流放大系数表示(共基极组态是α和共发射极组态是β)。对于共基极组态有:Ic=α Ie;对于共发射极组态有:Ic=β Ib。

对于共发射极组态的BJT,即使输入端(基极)开路,由于仍然保持为发射结正偏、集电结反偏,故也同样具有放大作用,即可把集电结反向饱和电流Ibco放大成βIbco、而输出所谓较大的穿透电流Ieco=Ibco β Ibco=(1 β)Ibco。

并且,只要是发射结正偏,即使集电结0偏,BJT也仍然处于放大状态。因为集电结中本来就存在较强的内建电场,反偏的效果只不过是增强其中的电场而已,并不改变集电结收集载流子的能力,所以在发射结正偏、集电结0偏时也具有放大作用。自然,当集电结电压稍微变为正偏时,BJT即转变为饱和状态了(输出电流不再与输入电流成正比);因此,发射结正偏、集电结0偏的状态又称为临界饱和状态。

此外,在发射结0偏(即发射极-基极短路)、集电结反偏时,晶体管同样处于放大状态,只不过这时被放大的电流是集电结反向饱和电流Ibco的一部分,所以输出电流很小(小于Ieco,大于Ibco)。

可见,只要晶体管的发射极有电流进入、集电极有正比于输入电流的电流输出时,那么该晶体管就处于放大状态。所以,即使集电结0偏(发射结正偏)或者发射结0偏(集电结反偏)时,晶体管都将处于放大状态。

BJT的放大性能,也可以采用所谓跨导gm来表示。因为gm=dIc/dVeb≈dIe/dVeb,所以BJT的跨导实际上也就近似为BJT的输入电导;而BJT的输入电导很大(≈qIe/kT),而且与输出电流成正比,故BJT具有很大的跨导,这一点对于BJT的模拟应用,远优于场效应晶体管,具有重要的价值。

(2)对于FET(包括JFET和MOSFET等):

因为FET是依靠沟道中的多数载流子来工作的器件,因此,只要是存在沟道,就具有放大作用。在有沟道、并且沟道又没有被夹断的状态(即为线性工作状态),是一种放大工作模式;同时在有沟道、并且沟道又被夹断了的状态(即为饱和工作状态),也是一种放大工作模式。因为FET是电压控制的器件,故放大状态的输出电流与输入电压成正比。放大性能用所谓栅极跨导(等于输出电流对栅极电压的微分)表示。

由于饱和放大状态工作的跨导最大(大于线性的放大工作模式),所以常常采用饱和模式来放大;在输出伏安特性曲线上也就是选用电流饱和的区域。

因为FET的输出电流与输入电压(栅极电压)是抛物线关系,不像BJT那样是指数函数关系,所以FET的跨导要小于BJT的跨导。从这一点来看,FET将不利于模拟应用;不过,对于MOSFET及其IC来说,由于Si平面工艺的优越性,使得FET也同样在模拟领域中被大量应用(特别是CMOS模拟电路的发展势头很好)。

☆晶体管的饱和状态----------

饱和状态就是晶体管的一种低电压、大电流工作状态(即开态).对于BJT(双极型晶体管)和对于FET(场效应晶体管),饱和状态的含义大不相同,要特别注意区分开来.

(1)对于BJT:

因为BJT是电流驱动的器件,则其饱和状态就是指电流较大、而电压饱和(基本恒定不变)的一种工作模式.BJT在饱和状态工作时,发射结和集电结都处于正偏,则导电很好、电流较大,这时输出的集电极电流Ic只决定于外电路的参量(Ic=Vcc/RL,式中的Vcc是电源电压,RL是负载电阻),而与输入电流无关(即这时已离开了放大状态);该状态是输出电流大、输出电压低的工作模式,相应于开关的开态.

在BJT的发射结正偏、集电结0偏时,晶体管仍然处于放大状态(输出电流正比于输入电流),但只要集电结电压稍微增大一点而正偏的话,那么晶体管就进入到饱和状态(输出电流与输入电流无关,只见对于外电路参数)。因此把BJT这种发射结正偏、集电结0偏的状态特称为临界饱和状态。

在BJT的输出伏安特性曲线上,饱和状态即是处在紧靠纵轴(电流轴)的一个小范围内.BJT在饱和状态工作时,总是希望该饱和范围越小越好,即要求输出电压——饱和压降越低越好.因为饱和压降直接关系到集电极串联电阻,故为了降低饱和压降,就需要提高集电区掺杂浓度;但为了提高提高击穿电压,又需要减小集电区掺杂浓度,这是一个矛盾.为解决此矛盾,就发展出了外延片的技术,即是在低阻衬底上生长一层薄的较高电阻率的外延层,然后在外延层上制作BJT;对于集成电路中的BJT来说,因为所有的电极都需要从芯片表面引出,因此在外延的基础上,还需要通过在器件有源区下面加设低阻埋层来减小集电极串联电阻.总之,在集成电路芯片中采用外延层和埋层的目的,都是为了在保持较高击穿电压的条件下来减小集电极串联电阻、以降低饱和压降.

(2)对于FET(包括JFET和MOSFET等):

因为FET是电压驱动的器件,则其饱和状态就是指电压较大、而电流饱和(基本恒定不变)的一种工作模式.

对于增强型n-FET,在栅电压为0时不存在沟道,只有正的栅极电压大于阈值电压Vt时才出现沟道(故这时的阈值电压也称为“开启电压”);当“源漏电压Vds≥栅源电压Vgs减去开启电压Vt”时,沟道即在靠近漏极处被夹断,晶体管就进入饱和工作状态。饱和状态的输出电流基本上由未被夹断的沟道部分的电阻来决定。在不考虑沟道长度调制效应时,则输出电流与源-漏电压无关,即输出电流饱和;但是此饱和的输出电流要受到栅极电压控制(饱和时的栅极跨导最大)。在输出伏安特性曲线上,饱和状态即是处在电流饱和的区域(即特性曲线是水平的区域);实际上,FET的饱和状态也就是常常采用的一种放大工作的状态(这与BJT的工作状态名称不同),因为FET在饱和状态时的跨导最大。

对于耗尽型n-MOSFET,在栅电压为0时即存在电子导电的沟道,就是线性导通状态;只有加上一定的栅极电压(负电压)后才能使沟道消失(整个沟道夹断),这时的栅电压称为”夹断电压”Vp,也就是耗尽型FET的阈值电压,当“源漏电压Vds≥夹断电压Vp减去栅源电压Vgs”时,沟道即在靠近漏极处被夹断,晶体管就进入饱和导通状态,输出电流最大、并饱和,同时跨导也最高——放大工作区。

值得注意,FET在饱和状态时沟道的夹断与没有沟道是两回事。沟道在漏端被夹断后,并不是不能导电,因为夹断区实际上就是一个存在电场的耗尽区,只要载流子(多数载流子)一到达耗尽区边缘,就立即被电场扫到集电极而输出电流。所以,沟道在一端被夹断后的导电性能将更好(导电性决定于未被夹断的部分沟道),这与完全没有沟道的截止状态完全不同。此外,对于JFET,其线性导通和饱和导通的情况与MOSFET的相同。

对于JFET,其线性导通和饱和导通的情况与MOSFET的相同。对于JFET,其线性导通和饱和导通的情况与MOSFET的相同。总之,BJT的饱和状态是指低电压、大电流的状态(属于“开态”),FET的饱和状态是指电流最大、并且饱和的状态(属于“放大态”)。两者的含义有所不同。

☆晶体管截止状态----------

截止状态就是电流很小、基本上不导通的一种工作状态(工作模式).这种状态,不管是BJT(双极型晶体管),还是FET(场效应晶体管),都是一致的;在输出伏安特性曲线上,其范围都是处于最下面的小区域(紧靠横轴——电压轴).

(1)对于BJT:

BJT的截止状态就是发射结和集电极都是反偏的状态,输出电流当然很小;这是一种”关”态.在共基极组态中,该很小的输出电流也就是集电结的反向饱和电流Ibco;而在共发射极组态中,该很小的输出电流是E、C电极之间的所谓穿透电流Ieco.

Ieco要比Ibco大得多.因为Ieco实际上也就是基极开路时的E、C电极之间的电流;而对于共发射极组态来说,即使基极开路,但发射结上还是加有正向电压、集电结上加有反向电压,即BJT仍然是处于放大状态,只不过这时通过发射结的”输入电流”是很小的Ibco,因此输出的集电极电流Ic就应该是: Ic=Ibco βIbco=(1 β)Ibco.

(2)对于FET:

FET的截止状态就是没有沟道的状态,当然这时不会导电;通过的电流也就是漏结的反向饱和电流,非常小.这也是一种”关”态.

注意:FET的截止状态不同于其饱和状态(即放大状态).截止状态是根本不存在沟道的状态,而饱和状态是有沟道、但沟道在漏极一端被夹断了的状态;因此截止状态的输出电流很小,而饱和状态的输出电流很大.

此外,对于MOSFET,也要注意区分截止状态与亚阈状态这两种工作状态.亚阈状态是半导体表面多数载流子耗尽、能带弯曲,但又没有完全形成沟道的一种状态(又称为弱反型状态,这时耗尽层厚度尚未达到最大);因此在亚阈状态工作时,有较小的电流沿着表面流动、并受到栅极电压的控制,从而可用作为低功耗的开关.