Zen4微架构升级要点主要有以下几处:

●分支预测得到了升级

●更大的操作缓存

●更大的指令失效队列

●更大的整数/浮点寄存器文件

●更深的缓冲区贯穿核心

●浮点单元提供高能效AVX-512支持

●载入/存储效率提升

●二级缓存提升到1MB/8-Way

Zen4微架构在前端、执行引擎、载入/存储和缓存等方面都有明显的提升,还加入了可以大幅提升浮点性能的AVX-512指令集,期望在视频编解码、科学计算、AI加速方面可以获得极大的性能增幅。

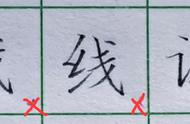

前端部分,Zen4着重提升了分支预测,从Zen3的每周期1个升级到2个,分支目标缓冲区(BTB)也随之提升,L1 BTB增大了50%(2×1K升级到2×1.5K),L2 BTB也增加了近8%(2×6.5K升级到2×7K)。操作缓存(Op Cache)增加了68%,而且每周期可以执行9条宏操作(Zen3是8个)。在整数和浮点之间提供每周期6条操作。

执行引擎部分,增大25%的失效指令队列,提供更大的整数/浮点寄存器文件和更深的缓冲区贯穿核心。实现每周期10个整数 6个浮点的发行带宽。

载入/存储部分,载入队列增大22%,数据缓存端口冲突进一步减少,L2 DTLB增大50%。每周期可完成3次内存操作,最高可实现3次载入、2次存储,提供6 Table Walkers。